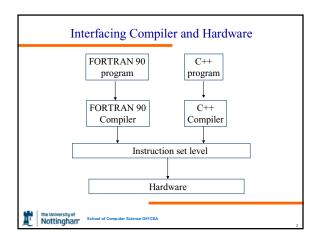

## **Computer Systems Architecture Processor Types** And **Instruction Sets** Nottingham

### What Instructions Should A Processor Offer?

- v Minimum set is sufficient, but inconvenient

- v Extremely large set is convenient, but inefficient

- v Architect must consider additional factors

- v Physical size of processor

- v Expected use

- v Power consumption

### **The Point About Instruction Sets**

The set of operations a processor provides represents a tradeoff among the cost of the hardware, the convenience for a programmer, and engineering considerations such as power consumption.

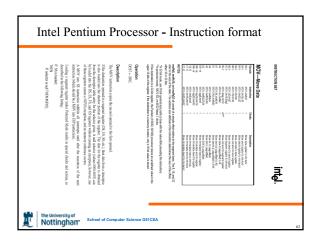

### Representation

- v Architect must choose

- v Set of instructions

- v Exact representation hardware uses for each instruction (instruction format)

- v Precise meaning when instruction executed

- v Above items define the instruction set

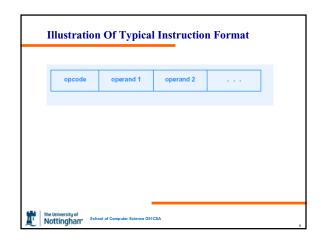

### Parts Of An Instruction

- v Opcode specifies instruction to be performed

- v Operands specify data values on which to operate

- v Result location specifies where result will be

- v Add X and Y, and place result in Z

- v Steps

- v Load a copy of X into register 3

- v Load a copy of Y into register 4

- v Add the value in register 3 to the value in register 4, and direct the result to register 5

- v Store a copy of the value in register 5 in Z

- v Note: assumes registers 3, 4, and 5 are free

### **Types Of Instruction Sets**

- v Two basic forms

- v Complex Instruction Set Computer (CISC)

- v Reduced Instruction Set Computer (RISC)

### **CISC Instruction Set**

- v Many instructions (often hundreds)

- v Given instruction can require arbitrary time to compute

- v Examples of CISC instructions

- v Move graphical item on bitmapped display

- v Memory copy or clear

- v Floating point computation

### **RISC Instruction Set**

- v Few instructions (typically 32 or 64)

- v Each instruction executes in one clock cycle

- v Example: MIPS instruction set

Nottinghan School of Computer Scie

### **Summary Of Instruction Sets**

A processor is classified as CISC if the instruction set contains instructions that perform complex computations that can require long times; a processor is classified as RISC if it contains a small number of instructions that can each execute in one clock cycle.

Nottingham School of Computer Science G51CSA

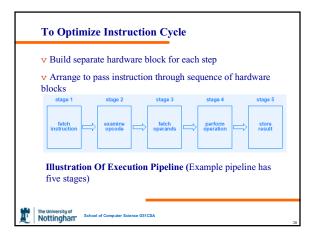

### **Execution Pipeline**

- v Hardware optimization technique

- v Allows processor to complete instructions faster

- v Typically used with RISC instruction set

Nottingham School of Computer Science G51CSA

Nottingham

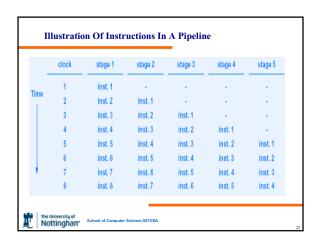

# Although a RISC processor cannot perform all steps of the fetch-execute cycle in a single clock cycle, an instruction pipeline with parallel hardware provides approximately the same performance: once the pipeline is full, one instruction completes on every clock cycle.

### **Example Of Instruction Stalls**

- v Assume

- v Need to perform addition and subtraction operations

- $\mathbf{v}$  Operands and results in register A through E

- v Code is:

Instruction K:  $C \leftarrow add A B$

Instruction K+1: D  $\leftarrow$  subtract E C

v Second instruction stalls to wait for operand C

### A Note About Pipelines

Although hardware that uses an instruction pipeline will not run at full speed unless programs are written to accommodate the pipeline, a programmer can choose to ignore pipelining and assume the hardware will automatically increase speed whenever possible.

### **No-Op Instructions**

- v Have no effect on

- v Registers

- v Memory

- v Program counter

- v Computation

- v Documents an instruction stall

Nottingham School of Computer Science G51CSA

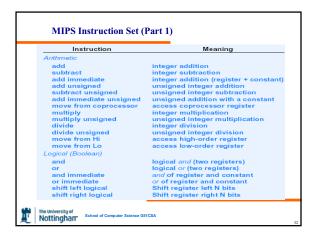

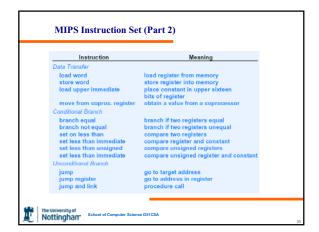

### **Types Of Operations**

- v One possible categorization

- v Arithmetic instructions (integer arithmetic)

- v Logical instructions (also called Boolean)

- v Data access and transfer instructions

- v Conditional and unconditional branch instructions

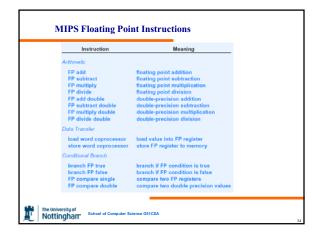

- v Floating point instructions

- v Processor control instructions

Nottingham School of Computer Science G51CSA

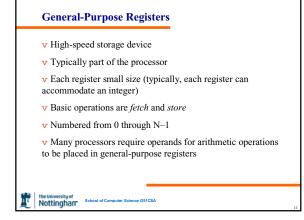

### **Program Counter**

- v Hardware register

- v Used during fetch-execute cycle

- v Gives address of next instruction to execute

- v Also known as instruction pointer

Nottingham School of Computer Science G51CSA

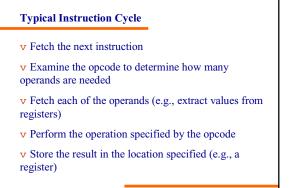

### Fetch-Execute Algorithm Details

Assign the program counter an initial program address.

Repeat forever {

Access the next step of the program from the location given by

Set an internal address register, A, to the address beyond the instruction that was just fetched.

### Execute:

Perform the step of the program.

Copy the contents of address register A to the program counter.

Nottingham School of Computer Science G51CSA

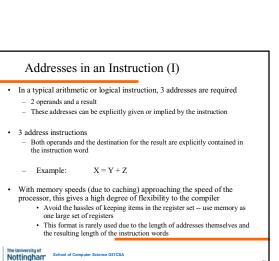

### Addresses in an Instruction (II)

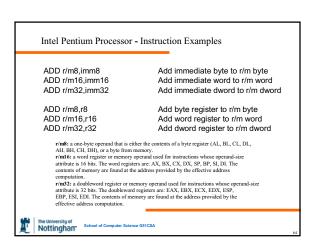

- · 2 address instructions

- One of the addresses is used to specify both an operand and the result location

Example: X = X + Y

Very common in instruction sets

- · 1 address instructions

- Two addresses are implied in the instruction

- Traditional accumulator-based operations Example: Acc = Acc + X

Nottingham School of Computer Science G51CSA

### Addresses in an Instruction (III)

- · 0 address instructions

- All addresses are implied, as in register-based operations

Example: TBA (transfer register B to A)

- · Stack-based operations

- All operations are based on the use of a stack in memory to store

- Interact with the stack using push and pop operations

Nottingham School of Computer Science G51CSA

### Addresses in an Instruction (IV)

- · Trade off:

- Fewer addresses in the instruction results in

- – More primitive instructions

- - Less complex CPU

- - Instructions with shorter length

- - More total instructions in a program

- - Longer, more complex programs

- - Longer execution time

Nottinghar School of Computer Science G51CSA

### Addresses in an Instruction (V)

Consider Y = (A-B) / (C+D\*E)

### 3 address

SUB Y,A,B MUL T,D,E ADD T.T.C DIV Y.Y.T

### 2 address

MOV Y,A SUB Y,B MOV T,D MUL T,E ADD T,C DIV Y,T

### 1 address

LOAD D MUL E ADD C STORE Y LOAD A SUB B DIV Y STORE Y

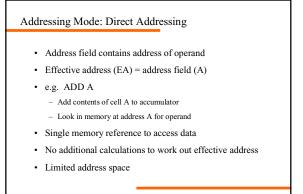

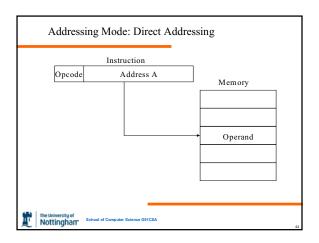

### Addressing Mode

- Once we have determined the number of addresses contained in an instruction, the manner in which each address field specifies memory location must be

- Want the ability to reference a large range of address locations

- Tradeoff between

- Addressing range and flexibility

- Complexity of the address calculation

Nottingham School of Computer Science G51CSA

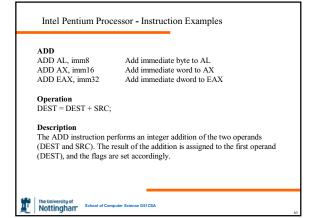

### Addressing Mode: Immediate Mode

- · The operand is contained within the instruction itself

- · Data is a constant at run time

- No additional memory references are required after the fetch of the instruction itself

- · Fast, but size of the operand (thus its range of values) is limited

e.g. ADD 5

Add 5 to contents of accumulator 5 is operand

Operand

Instruction Opcode

Nottinghar School of Cor

The University of Nottingham School of Computer Science G51CSA

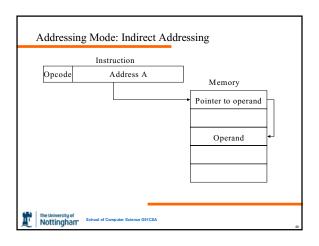

## The address field in the instruction specifies a memory location which contains the address of the data Two memory accesses are required The first to fetch the effective address The second to fetch the operand itself Range of effective addresses is equal to 2<sup>n</sup>, where n is the width of the memory data word Number of locations that can be used to hold the effective address is constrained to 2<sup>k</sup>, where k is the width of the instruction's address field